Quite a lot of operations are done for ‘preparedness’.

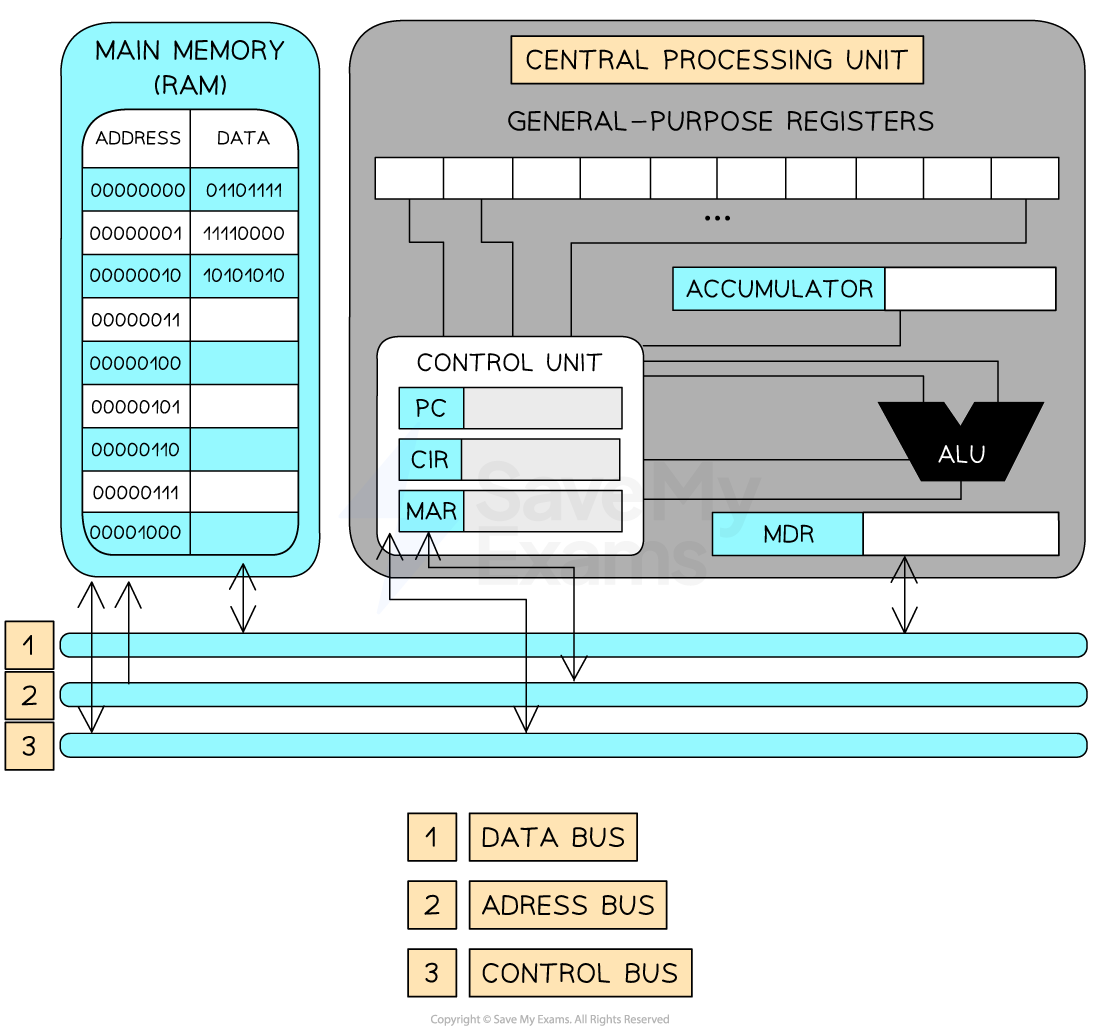

Memory Data Register (MDR)

also known as the Memory Buffer Register (MBR).

- Communicates with the RAM over the data bus, sets and retrieves (MDR ↔ RAM)

- Holds the data (temporarily) which is read from/written to memory

- All data to and from memory must travel down the data bus ad pass through the MDR

Memory Address Register (MAR)

- Communicates with the RAM over the address bus, only sets (MAR → RAM)

- Holds the address of the memory location from which data/an instruction is to be fetched/written to

Program Counter (PC)

- Holds the address of the next instruction to be executed

- Has a very close relationship with the MAR

- At the start of every new fetch-execute-cycle, the address held in the PC is copied to the MAR

- Looks forward

Examples

- The next instruction in a sequence

- The address to jump to if the current instruction is a jump/branch - this is copied from the CIR

Accumulator

- A general purpose register

- Data or control information is often stored here

- A CPU may have many general purpose registers for storing temporary data while instructions or calculations are being carried out

- Typically, the more general purpose registers a processor has, the faster it may operate

- The results of calculations by the ALU may be temporarily stored here

Arithmetic Logic Unit (ALU)

- Performs arithmetic and logical operations on data

- Arithmetic operations on fixed/floating point numbers

- ADD

- SUBTRACT

- MULTIPLY

- DIVIDE

- Bitwise shift operations

- Boolean logic operations

- COMPARISON

- AND

- OR

- NOT

- XOR

- Often uses general purpose registers to temporarily hold the results of calculations such as the accumulator

Current Instruction Register (CIR)

- Holds the current instruction being executed

- The contents of the MDR are copied to the the CIR if it is an instruction

- Contains the opcode and operand(s) of the current instruction

Control Unit (CU)

Imagine it as a traffic warden. 🚦

- Communicates with the RAM over the control bus, only sets (MAR → RAM)

- Coordinates all activities on the CPU

- Accepts the next instruction, decodes it, handles its execution, stores the resulting data back in memory or registers

- Sends memory read and write requests to main memory on the control bus, as well as other command and control signals such as bus requests, bus grants, interrupt requests, etc.

- Makes extensive use of the status registers and clock

Cache

Buses

- Multiple buses are used to work in parallel and for maximum possible speed (avoidance of bottlenecking)

Address Bus

- Carries memory addresses that identify where the data is being read from or written to (uni-directional)

Data Bus

- Carries the binary data that make up the actual information being transmitted around the CPU/computer

Control Bus

- Carries command and control signals to and from every other component of the CPU/computer